服务热线: 0755-83261303

地址:深圳市龙华区大浪街道浪口社区华昌路315号华昌工业园

芯片中的CP是什么CP

发表时间:2022-07-12

发表时间:2022-07-12 浏览量: 8468

浏览量: 8468

芯片中的CP一般指的是CP测试,也就是晶圆测试(Chip Probing)。

一、CP测试是什么

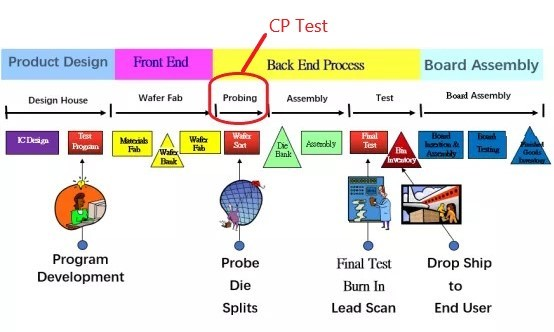

CP测试在整个芯片制作流程中处于晶圆制造和封装之间,测试对象是针对整片晶圆(Wafer)中的每一个Die,目的是确保整片(Wafer)中的每一个Die都能基本满足器件的特征或者设计规格书,通常包括电压、电流、时序和功能的验证。

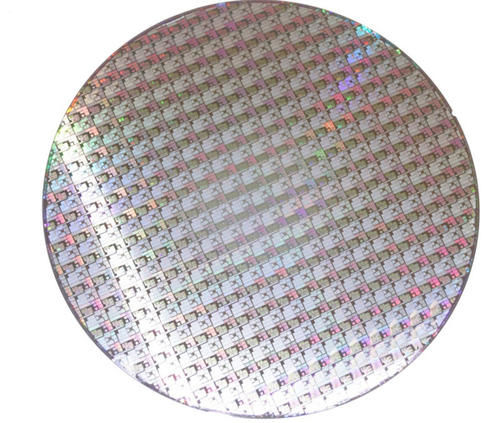

CP测试的具体操作是在晶圆制作完成之后,成千上万的裸DIE(未封装的芯片)规则的分布满整个Wafer。由于尚未进行划片封装,只需要将这些裸露在外的芯片管脚,通过探针(Probe)与测试机台(Tester)连接,进行芯片测试就是CP测试。

图 1 CP Test在芯片产业价值链上的位置

二、为什么要做CP测试

因为通常在芯片封装阶段时,有些管脚会被封装在芯片内部,导致有些功能无法在封装后进行测试,因此Wafer中进行CP测试最为合适。

图 2 Wafer上规则的排列着DIE

而且Wafer制作完成之后,由于工艺偏差、设备故障等原因引起的制造缺陷,分布在Wafer上的裸DIE中会有一定量的残次品。CP测试的目的就是在封装前将这些残次品找出来(Wafer Sort),同时还可以避免被封装后无法测试芯片性能,优化生产流程,简化步骤,同时提高出厂的良品率,缩减后续封装测试的成本。

另外,有些公司会根据CP测试的结果,将芯片划分等级,将这些产品投入不同的市场,购买者需要注意这一点。

三、测试内容有哪些

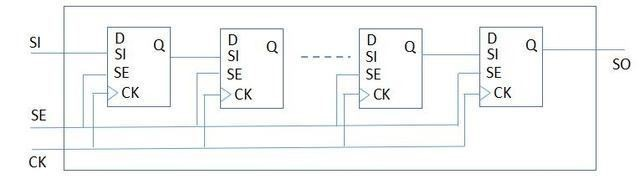

1、SCAN

SCAN用于检测芯片逻辑功能是否正确。DFT设计时,先使用DesignCompiler插入ScanChain,再利用ATPG(Automatic Test Pattern Generation)自动生成SCAN测试向量。SCAN测试时,先进入Scan Shift模式,ATE将pattern加载到寄存器上,再通过Scan Capture模式,将结果捕捉。再进入下次Shift模式时,将结果输出到ATE进行比较。

图 3 Scan Chain示意图

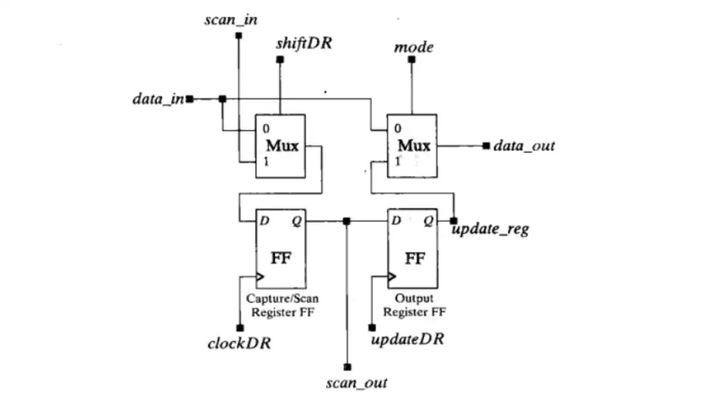

2、Boundary SCAN

Boundary SCAN用于检测芯片管脚功能是否正确。与SCAN类似,Boundary SCAN通过在IO管脚间插入边界寄存器(Boundary Register),使用JTAG接口来控制,监测管脚的输入输入出状态。

图 4 Boundary Scan原理图

四、测试方法有哪些

1、DC/AC Test

DC测试包括芯片Signal PIN的Open/Short测试,电源PIN的PowerShort测试,以及检测芯片直流电流和电压参数是否符合设计规格。AC测试检测芯片交流信号质量和时序参数是否符合设计规格。

2、RF Test

对于无线通信芯片,RF的功能和性能至关重要。CP中对RF测试来检测RF模块逻辑功能是否正确。

3、存储器

存储器测试数量较大,因为芯片往往集成着各种类型的存储器(例如ROM/RAM/Flash),为了测试存储器读写和存储功能,通常在设计时提前加入BIST(Built-In SelfTest)逻辑,用于存储器自测。芯片通过特殊的管脚配置进入各类BIST功能,完成自测试后BIST模块将测试结果反馈给Tester。

(1)ROM(Read-Only Memory)通过读取数据进行CRC校验来检测存储内容是否正确。

(2)RAM(Random-Access Memory)通过除检测读写和存储功能外,有些测试还覆盖DeepSleep的Retention功能和Margin Write/Read等等。

(3)Embedded Flash除了正常读写和存储功能外,还要测试擦除功能。

(4)Wafer还需要经过Baking烘烤和Stress加压来检测Flash的Retention是否正常。

(5)还有Margin Write/Read、Punch Through测试等等。

4、其他Function Test

芯片其他功能测试,用于检测芯片其他重要的功能和性能是否符合设计规格。

随着芯片工艺越来越先进,晶体管密度越来越高,芯片测试的复杂度和难度也成倍地增长。本文金誉半导体只梳理了一些梳理基本的测试概念,和简单基础的CP测试知识,后续我们会再针对这个话题进行一些更加全面的探讨。